作者 | ZeR0

编辑 | 漠影

芯东西3月28日报道,近日,英特尔先进系统封装与测试事业部副总裁兼总经理Mark Gardner分享了英特尔半导体先进封装技术最新进展。

半导体先进封装技术能够在单个设备内集成不同功能、制程、尺寸、厂商的芯粒(chiplet),以灵活性强、能效比高、成本经济的方式打造系统级芯片(SoC),因此受到越来越多的AI芯片厂商青睐。

Mark Gardner认为,当前我们正处于一个由AI驱动的范式转换之中,这种转变在复杂度和价值方面具有显著影响。随着这一转变进行,系统级代工厂以及系统技术协同优化的概念变得愈发重要,涵盖了更多系统级的创新。

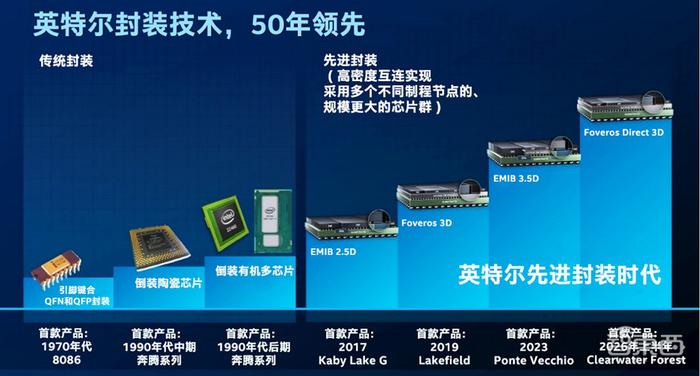

英特尔自本世纪70年代起持续创新,深耕封装技术,积累了超过50年的丰富经验。

面向AI时代,英特尔正在与生态系统伙伴、基板供应商合作,共同制定标准,引领整个行业应用先进封装技术。秉持“系统工艺协同优化”(STCO)的理念,英特尔代工不仅能够向客户提供传统的封装、互连、基板等技术,还涵盖了系统级架构和设计服务,以及热管理和功耗管理等全方位支持工作。

自20世纪70年代和80年代以来,英特尔一直在封装技术领域处于领先地位,包括引线键合架构(Wire-Bond QFN/QFP)、倒装陶瓷芯片(Flip-Chip Ceramic)、倒装有机多芯片(Flip-Chip Organic & Multi-Chip)等传统封装形式。

现在,英特尔通过与生态系统合作伙伴合作,共同制定标准,与基板供应商协作,引领整个生态系统和行业进入先进封装时代。

先进封装包括2.5D、3D以及如今的3.5D封装技术。这些技术是长期发展的结果。EMIB 2.5D的首个产品已经投产近十年了,3D和3.5D堆叠原理逐渐落地应用。Mark Gardner承诺,英特尔将在AI时代不断创新,继续成为先进封装领域的领导者。

一、丰富全面的技术组合:解读六大关键技术

英特尔代工的先进系统封装及测试(Intel Foundry ASAT)的技术组合,包括FCBGA 2D、FCBGA 2D+、EMIB 2.5D、EMIB 3.5D、Foveros 2.5D & 3D和Foveros Direct 3D等多种技术。

▲左上:FCBGA 2D、右上:EMIB 2.5D、左下:Foveros 2.5D & 3D、右下:EMIB 3.5D

▲左上:FCBGA 2D、右上:EMIB 2.5D、左下:Foveros 2.5D & 3D、右下:EMIB 3.5D(1)FCBGA 2D:是传统的有机FCBGA(倒装芯片球栅格阵列)封装,适用于成本敏感、I/O数量较少的产品。

(2)FCBGA 2D+:在此基础上增加了基板层叠技术(substrate stacking),能够减少高密度互连的面积,降低成本,特别适合网络和交换设备等产品。

(3)EMIB(嵌入式多芯片互连桥接)2.5D:通过基板内的微型硅桥连接芯片,适用于高密度的芯片间连接,在AI和高性能计算(HPC)领域表现出色。

(4)EMIB 3.5D:在此基础上引入了3D堆叠技术,芯片可以垂直堆叠在有源或无源的基板上,再通过EMIB技术连接,增加了堆叠的灵活性,能够根据IP的特性选择垂直或水平堆叠,同时避免使用大型的中介层。

(5)Foveros 2.5D和3D:采用基于焊料的连接方式,而不是基底连接,适合高速I/O与较小芯片组分离的设计。

(6)Foveros Direct 3D:通过铜和铜直接键合,实现更高的互连带宽和更低的功耗,从而提供卓越的性能。

这些技术并非互斥,而是在一个封装中可以同时采用,为复杂芯片的设计提供了极大的灵活性。在商业层面,这体现了英特尔对封装细分市场的重视。

二、为什么EMIB是AI芯片封装的理想选择?

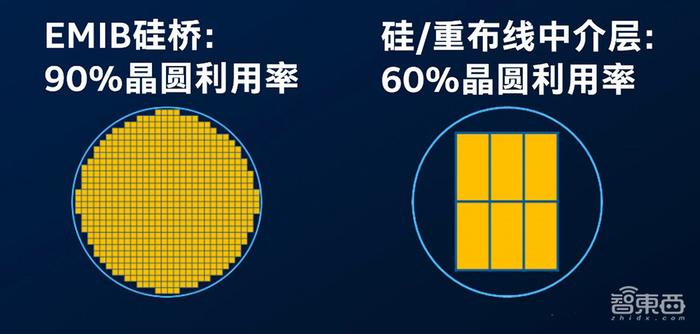

针对AI芯片的先进封装需求,与业界其它晶圆级2.5D技术,例如硅中介层、重布线层(RDL)相比,EMIB 2.5D技术具有诸多优势。

第一,成本效益。EMIB技术采用的硅桥尺寸非常小,相比于传统的大尺寸中介层,制造时能更高效地利用晶圆面积,减少空间和资源的浪费,综合成本更低。

第二,良率提升。EMIB技术省略了晶圆级封装(wafer level assembly)这一步骤,减少了模具、凸点等复杂工艺带来的良率损失风险,从而提高了整体生产过程的良率。

第三,生产效率。与晶圆级技术相比,EMIB技术的制造步骤更少、复杂度更低,因此生产周期更短,能够为客户节省宝贵的时间。在市场动态快速变化的情况下,这种时间优势能够帮助客户更快地获得产品验证数据,加速产品上市。

第四,尺寸优化。晶圆级技术需要在基板上方添加中介层,而EMIB则将硅桥嵌入基板,极大地提高了基板面积的利用率。同时,基板的尺寸与集成电路面板的格式相匹配,采用EMIB能够在单个封装中集成更多芯片,从而容纳更多的工作负载。

第五,供应链与产能。英特尔拥有成熟的供应链和充足的产能,确保了EMIB能够满足客户对先进封装解决方案的需求。

三、预留充足产能空间,覆盖从消费级到数据中心产品

Mark Gardner谈道,过去几年,行业在2.5D封装产能方面确实面临诸多限制,甚至抑制了市场需求,但英特尔代工在这一领域拥有显著优势,将Foveros 2.5D与EMIB 2.5D的产能相结合时,其综合产能是当前行业水平的两倍以上,并预留了充足的空间来支持未来的需求增长。

英特尔已经完成了超过250个2.5D设计项目,这些项目既涉及英特尔产品,也涵盖其他无晶圆厂客户的需求。这些设计需要不同面积,不同数量芯片的封装,应用范围从消费级产品到FPGA、服务器数据中心以及AI加速器。

在额外增值服务方面,英特尔可以帮助客户优化产品,无论是硅与封装的协同设计、设计策略,还是功率传输、高级建模和热管理等方面。此外,英特尔对不同材料进行了广泛的实验室表征,可以与客户合作并提供反馈,以帮助改进产品。

针对芯片测试,英特尔“裸片测试”(Die Sort)技术已在生产中使用了十多年。英特尔会将整片晶圆分割成一个个单独的裸片,并在组装到基板之前对它们进行分类和测试。

因裸片体积较小,热量控制可以非常精确,热管理能力显著增强。例如,这一过程可以实现温度在1秒内变化约100摄氏度。这种精确的热控制使得过去只能在最终测试阶段执行的内容,现在可以提前在裸片测试阶段完成,因而能够更早地识别出哪些GPU或计算单元有缺陷,显著提升生产效率和良率。

在今天,当封装的材料成本加上所有硅片内容达到数千美元时,这种改进尤为关键。

英特尔团队发现,通过在制造过程中加入测试环节,可以在不同阶段进行质量检测,而无需等到最后阶段。

如今,一款产品可能包含10片、20片、30片甚至50片芯片,在投入更多组件之前,确保之前的封装步骤制造的都是已知良品的良品管理,比以往更加重要。

结语:正在研发120×120毫米超大封装,未来几年推出玻璃基板

总体来看,英特尔半导体先进封装采用了多元措施,形成系统协同。比如用模拟裸片测试来优化良品管理,采用基于热压结合的EMIB技术来降本增效,引入Foveros Direct技术优化互连等等。

随着技术发展,封装尺寸变得越来越大,并且出现了较大的翘曲问题。因此英特尔引入了一系列创新技术,以便能够在翘曲情况下仍能顺利进行板级封装(Board Assembly)。

面向未来,英特尔正在研发120×120毫米的超大封装(Large Packages),并计划在未来几年内向市场推出玻璃基板(glass substrate)。

与目前采用的有机基板相比,玻璃基板具有超低平面度、更好的热稳定性和机械稳定性等独特性能,能够大幅提高基板上的互连密度,为AI芯片的封装带来新的突破。

硅封装协同设计是一个需要反复迭代的复杂过程。凭借英特尔的架构设计能力,英特尔能够与客户密切合作,提供最优的解决方案。这些举措共同构建了一个差异化的AI产品系统。

英特尔在晶圆制造层面也采取了相同的策略。这种灵活性使其能够根据客户的需求,提供最有价值的服务,并使用户能够专注于他们认为对自身业务最重要的环节。

长期以来,英特尔一直与台积电、三星等其他代工厂合作,并制定了兼容的设计规则,以确保这些代工厂生产的晶圆可以与英特尔的封装技术兼容。这使客户能够自由组合不同供应商的技术。

如今英特尔代工调整了策略,提供更灵活的服务。例如客户可以仅选择英特尔的EMIB技术或封装服务,而芯片部分则来自其他代工厂,也可以只采用英特尔的测试方案。

英特尔在AI时代的先进封装技术领域不断创新,将继续引领和推动行业发展,为全球半导体产业注入新的活力。

4000520066 欢迎批评指正

All Rights Reserved 新浪公司 版权所有